Datasheet 搜索 > 编解码器 > ADI(亚德诺) > AD1938WBSTZ 数据手册 > AD1938WBSTZ 产品设计参考手册 4/32 页

器件3D模型

器件3D模型¥ 22.778

AD1938WBSTZ 产品设计参考手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

编解码器

封装:

LQFP-48

描述:

ANALOG DEVICES AD1938WBSTZ 音频编解码器, AEC-Q100, 立体声, 4, 8, -40 °C, 105 °C, 192 kSPS

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P9P10P11P12P13P14P15P16P17

型号编码规则在P26

导航目录

AD1938WBSTZ数据手册

Page:

of 32 Go

若手册格式错乱,请下载阅览PDF原文件

UG-045 Evaluation Board User Guide

Rev. 0 | Page 4 of 32

08421-005

JP5

AVDD2

AVDD1

DVDD

JP6 JP7

POWER SELECTION

Figure 5. AD1938 Power Jumpers

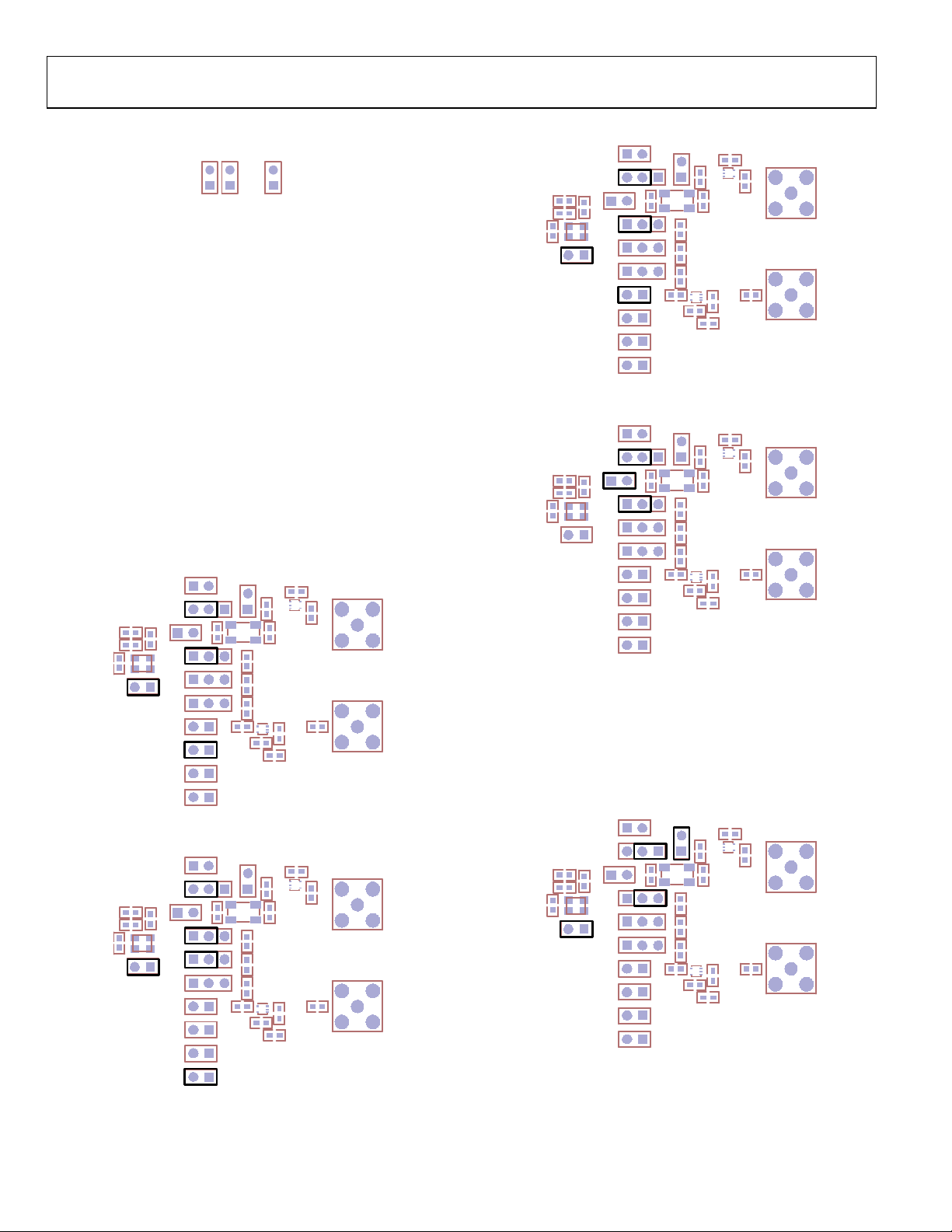

SETTING UP THE MASTER CLOCK (MCLK)

The evaluation board has a series of jumpers that give the user

great flexibility in the MCLK clock source for the AD1938.

MCLK can come from six different sources: passive crystal,

active oscillator, external clock in, S/PDIF receiver, and two

header connections. Note that the complex programmable logic

device (CPLD) on the board must have a valid clock source; the

frequency is not critical. These jumper blocks can assign the

CPLD clock as well. Most applications of the board use MCLK

from either the S/PDIF receiver or one of the header (HDR)

inputs. Figure 6 to Figure 9 show the on-board active oscillator

disabled so that it does not interfere with the selected clock. The

clock feed to the CPLD comes directly from the clock source.

Note that, if the HDR connectors are to be driven with MCLK

from a source on the evaluation board, SW2 and/or SW3 must

be switched from the IN position to the OUT position.

08421-006

JP31

HDR1

JP30

HDR2

JP29

8416

JP28

CLK

JP24

OSC

R155

R156

C154

C153

MCLKI

XTAL

MCLKO

XTAL

R166

R178

MCLKI BUS

MCLKO BUS

JP27

HDR1

JP25

HDR2

JP23

CPLD

OSC DISABLE

193X_MCLKI

DISABLE

EXT

EXT CLK IN

193X_MCLKO

1938_MCLKI

R160

R167

R169

R172

R174

R175

C168

C170

JP22

C158

L7

JP19

JP18 JP20

C147

U21

U18

U22

Y1

J23

J22

Figure 6. S/PDIF Receiver as MCLK Master; the AD1938 and CPLD as Slaves

08421-007

JP31

HDR1

JP30

HDR2

JP29

8416

JP28

CLK

JP24

OSC

R155

R156

C154

C153

MCLKI

XTAL

MCLKO

XTAL

R166

R178

MCLKI BUS

MCLKO BUS

JP27

HDR1

JP25

HDR2

JP23

CPLD

OSC DISABLE

193X_MCLKI

DISABLE

EXT

EXT CLK IN

193X_MCLKO

1938_MCLKI

R160

R167

R169

R172

R174

R175

C168

C170

JP22

C158

L7

JP19

JP18 JP20

C147

U21

U18

U22

Y1

J23

J22

Figure 7. HDR1 as MCLK Master; the AD1938, CPLD, and HDR2 as Slaves

08421-008

JP31

HDR1

JP30

HDR2

JP29

8416

JP28

CLK

JP24

OSC

R155

R156

C154

C153

MCLKI

XTAL

MCLKO

XTAL

R166

R178

MCLKI BUS

MCLKO BUS

JP27

HDR1

JP25

HDR2

JP23

CPLD

OSC DISABLE

193X_MCLKI

DISABLE

EXT

EXT CLK IN

193X_MCLKO

1938_MCLKI

R160

R167

R169

R172

R174

R175

C168

C170

JP22

C158

L7

JP19

JP18 JP20

C147

U21

U18

U22

Y1

J23

J22

Figure 8. External Clock In as Master; the AD1938 and CPLD as Slaves

08421-009

JP31

HDR1

JP30

HDR2

JP29

8416

JP28

CLK

JP24

OSC

R155

R156

C154

C153

MCLKI

XTAL

MCLKO

XTAL

R166

R178

MCLKI BUS

MCLKO BUS

JP27

HDR1

JP25

HDR2

JP23

CPLD

OSC DISABLE

193X_MCLKI

DISABLE

EXT

EXT CLK IN

193X_MCLKO

1938_MCLKI

R160

R167

R169

R172

R174

R175

C168

C170

JP22

C158

L7

JP19

JP18 JP20

C147

U21

U18

U22

Y1

J23

J22

Figure 9. Active On-Board Oscillator as Master; the AD1938 and

CPLD as Slaves

The MCLK configurations shown in Figure 10 and Figure 11 use

the AD1938 MCLKO port to drive the CPLD and, possibly, the

HDRs. The passive crystal runs the AD1938 at 12.288 MHz.

Figure 11 shows the MCLKI shut off; this is the case when the

PLL is set to LRCLK instead of MCLK.

08421-010

JP31

HDR1

JP30

HDR2

JP29

8416

JP28

CLK

JP24

OSC

R155

R156

C154

C153

MCLKI

XTAL

MCLKO

XTAL

R166

R178

MCLKI BUS

MCLKO BUS

JP27

HDR1

JP25

HDR2

JP23

CPLD

OSC DISABLE

193X_MCLKI

DISABLE

EXT

EXT CLK IN

193X_MCLKO

1938_MCLKI

R160

R167

R169

R172

R174

R175

C168

C170

JP22

C158

L7

JP19

JP18

JP20

C147

U21

U18

U22

Y1

J23

J22

Figure 10. Passive Crystal; AD1938 Is Master; CPLD Is Slave from

the MCLKO Port

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件